### Performance Contracts for Modular MPSoC Integration

Pieter van der Wolf NXP Semiconductors Research

MPSoC'08 June 23 - 27, 2008

## **SoC** integration

Today's practice

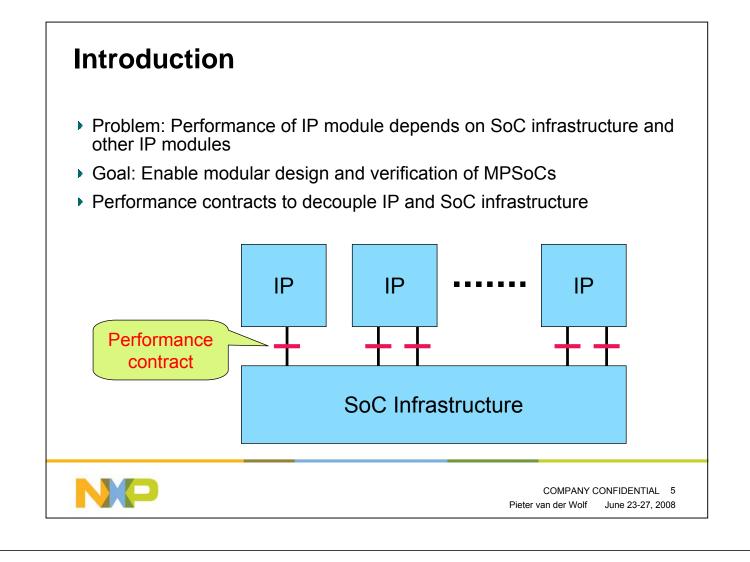

Complexity of SoC integration increasing

Communication requirements of IP modules often not explicit

Performance of one IP module influenced by other IP modules

What if you could ...

Explicitly express communication requirements of IP modules

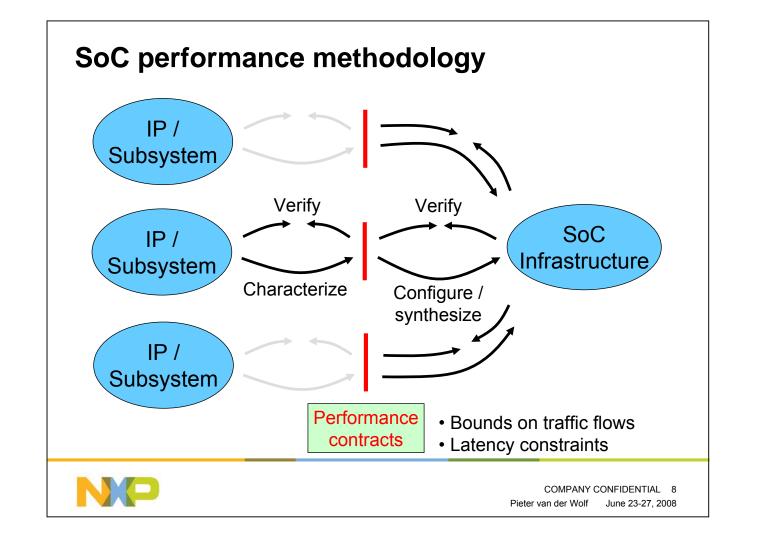

Independently verify performance of IP modules and SoC infrastructure

Reuse performance verification results when reusing IP modules

PHILIPS

## **Verification of IP modules**

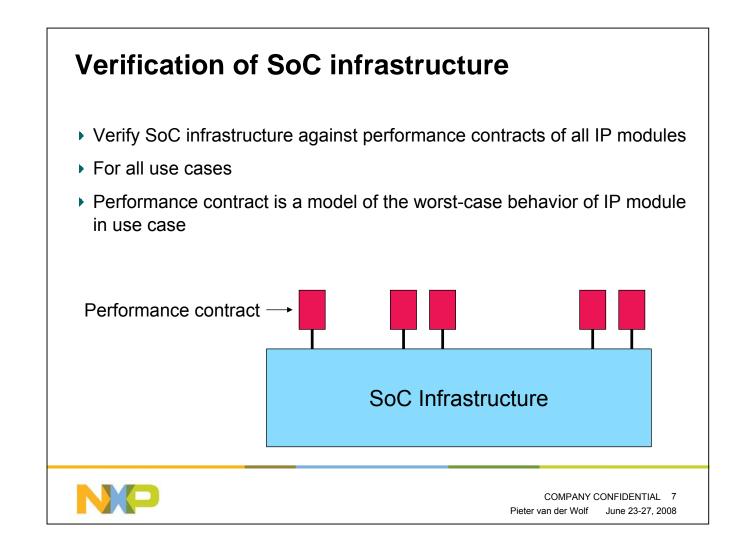

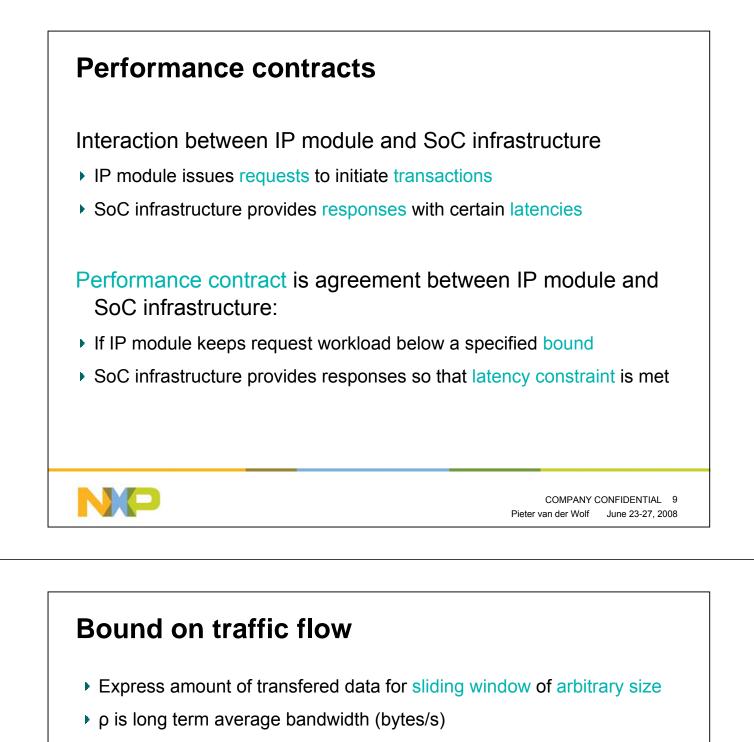

- Verify IP module against performance contract

- Will task executed on IP meet deadlines with performance contract ?

- Performance contract models worst-case behavior of SoC infrastructure

- Per interface (AXI, OCP) there can be more than one contract

- One IP module can have more than one interface

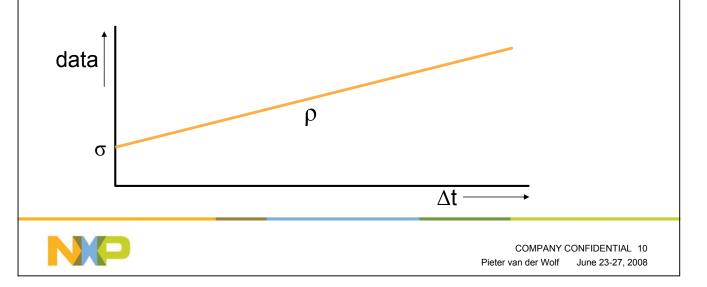

- σ is burstiness constraint (bytes)

- For every window of size  $\Delta t$ : data  $\leq \sigma + \rho * \Delta t$

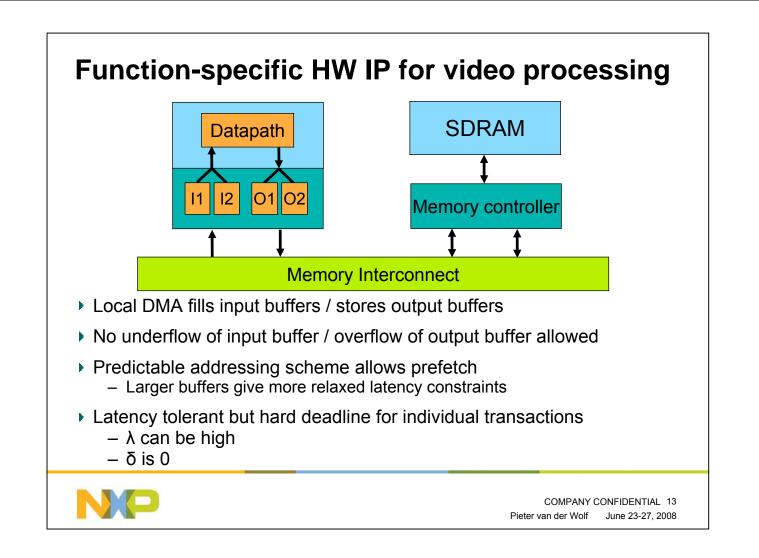

## **Programmable processor**

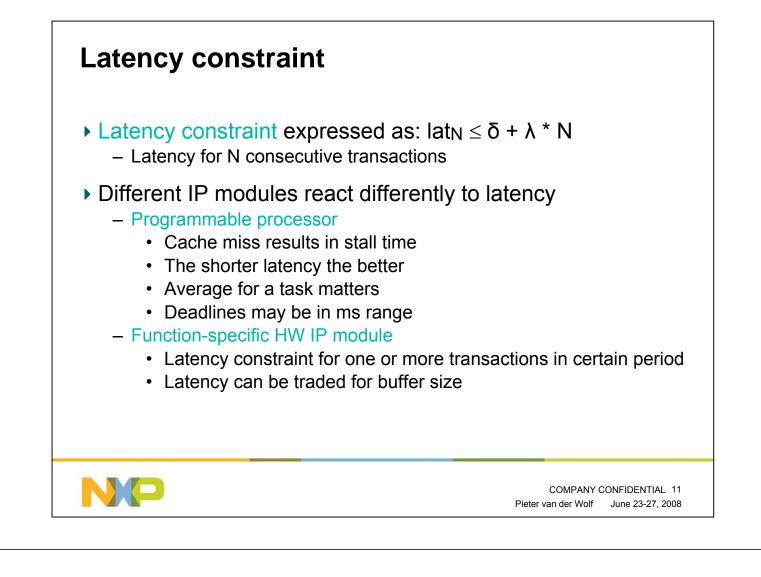

- Temporal distribution of requests largely unpredictable

- Data size corresponds to cache line (32 B 128 B)

- Processor stalls upon cache miss

- Low latency requirement

- Some (hardware or software) prefetch support to hide latency

- Deadlines at task-level often at millisecond timescale

- Latencies can be averaged out over set of transactions

- $-\delta$  can be high

- $-\lambda$  should be low

# Other parameters in performance contract

#### Degree

- Number of outstanding transactions allowed by SoC infrastructure

- If more than degree outstanding: service not guaranteed

- Forces IP to accept responses if it wants to maintain service

### Transaction sizes

- Size of transactions issued under performance contract

- For example specified as  ${\rm T}_{\rm max}$  and  ${\rm T}_{\rm min}$

- Distribution of transaction sizes

### **Contract parameters**

| Parameter        | Description                                |

|------------------|--------------------------------------------|

| σ                | Workload burstiness                        |

| ρ                | Workload long term average bandwidth       |

| δ                | Latency burstiness                         |

| λ                | Long term average latency                  |

| degree           | Maximum number of outstanding transactions |

| Transaction size | Transaction sizes (incl. distribution)     |

NP

COMPANY CONFIDENTIAL 15 Pieter van der Wolf June 23-27, 2008

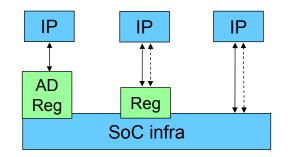

## Impact on interface protocols

- Distinguish multiple flows going over single hardware interface

- To allow explicit regulation of flows if IP does not comply

- To enable use of flow information in SoC infrastructure for QoS

- Two mechanisms

- Address discrimination (AD)

- Explicit identification of flows

- Extend interface protocols with optional flow identification

- So that different flows on interface can be distinguished

- Extension of AXI / OCP with flowID

## Conclusion

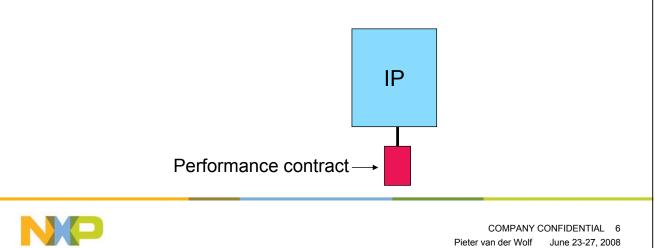

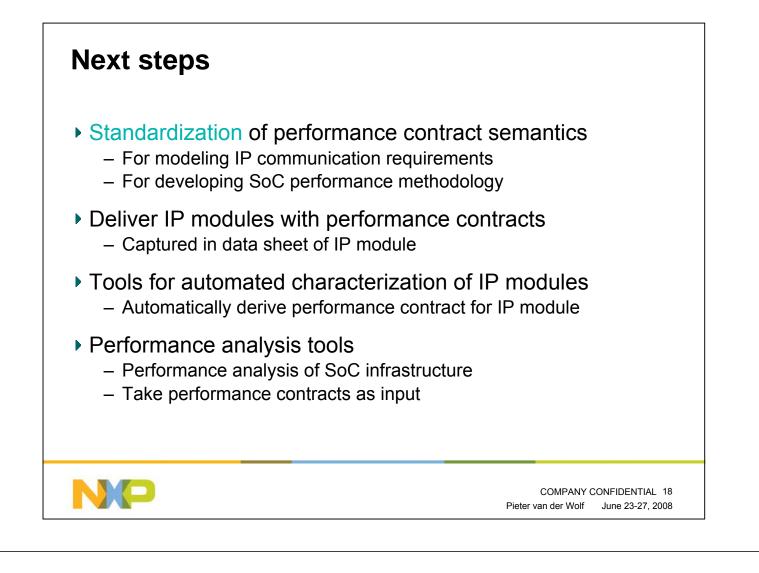

- Performance contract decouples IP modules and SoC infrastructure

- Key concept for modular integration of MPSoCs

- Central concept in SoC performance methodology

Facilitates use of formal techniques for SoC performance analysis

- Facilitates use of formal techniques for SoC performance analysis

- Need for further standardization

- To enable reuse of IP modules across companies

- To enable tool development by EDA vendors

### Acknowledgements

- Tomas Henriksson

- Axel Jantsch (KTH Sweden)

- Alistair Bruce (ARM Ltd)

- And many others ...

COMPANY CONFIDENTIAL 20 Pieter van der Wolf June 23-27, 2008